Trion 20 FPGA Configuration Time 줄이기 입니다.

T20BGA256 DevKit 을 활용하여 점검해 보았습니다.

Configuration Time 을 줄이는 방법에는 2가지가 있습니다.

1. Configuration Mode 변경.

2. SPI Programming Clock Divider 값 변경.

1. Configuration Mode 변경.

먼저 Trion 20 FPGA 의 Configuration Mode는 CBUS[2:0] 에 의해서 변경됩니다.

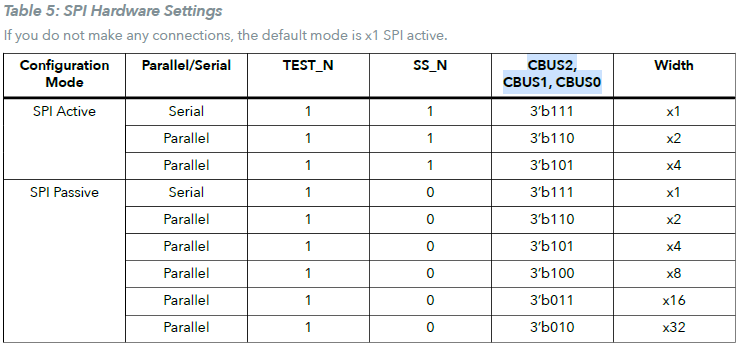

CBUS[2:0] 값에 따른 Configuration Mode 는 아래와 같습니다.

(참고문서 : https://www.efinixinc.com/docs/an006-configuring-trion-fpgas-v5.5.pdf )

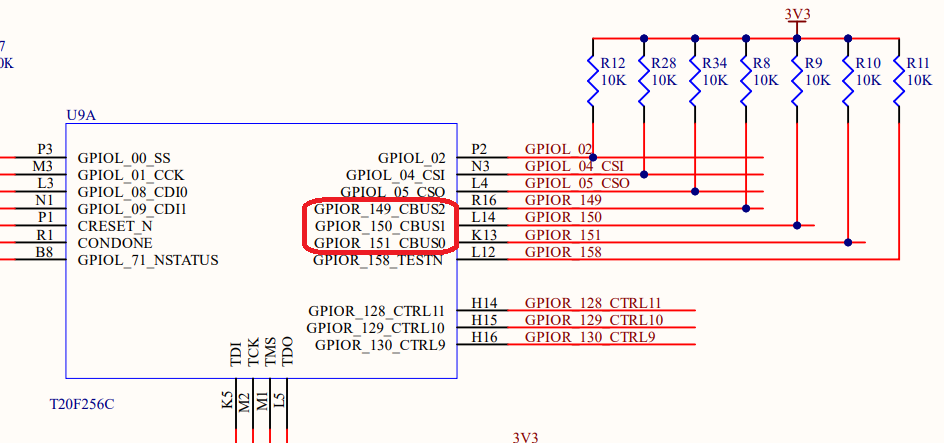

T20BGA256 DevKit 의 Schematic 을 확인해 보면 Configuratio Mode 가 CBUS[2:0] = 3'B111 (x1, Default) 인 것을 확인할 수 있습니다.

(참고문서 : https://www.efinixinc.com/docs/t20bga256-dev-board-schematics-rev3-v3.0.pdf )

T20BGA256 DevKit 의 R10(10 Kohm) 을 제거하고 K13 (GPIOR_151_CBUS0) 핀이 Pull-Down 이 되도록 점퍼를 날려 10 Kohm 저항을 붙여주면 Configuration Mode 를 CBUS[2:0] = 3'B110 (x2) 로 변경할 수 있습니다.

더불어, Configuratio Mode 에 맞추어 Bitstream File 생성 옵션을 변경해 주는 것이 필요합니다.

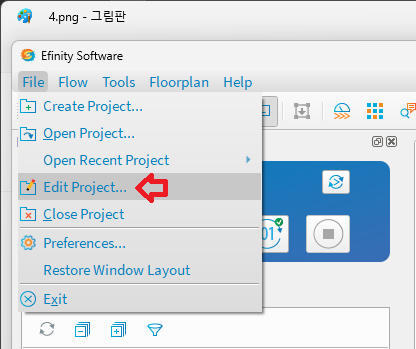

Efinity IDE 를 실행하여 기존에 생성해 놓은 프로젝트를 열어준 후 "File" -> "Edit Project..." 를 실행합니다.

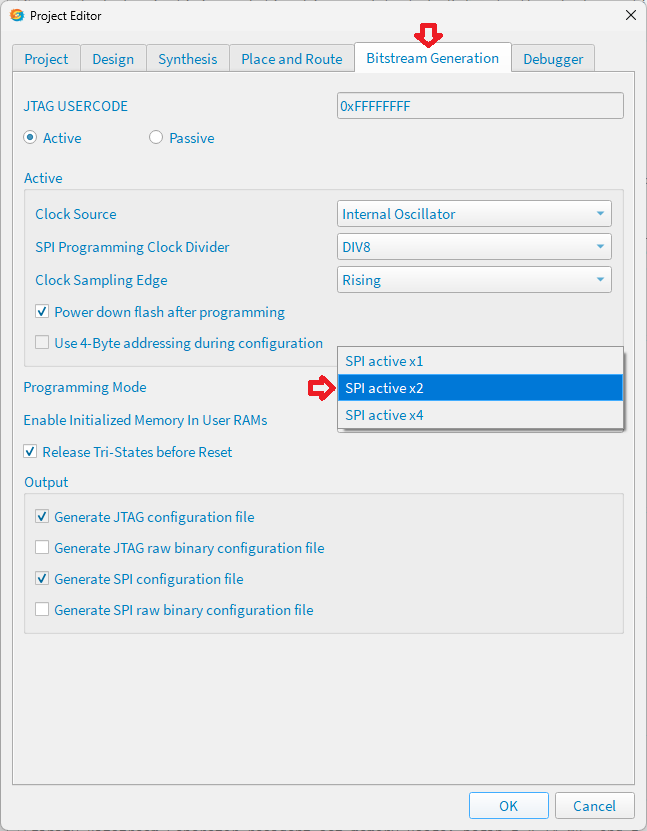

"Project Editor" 창이 열리면 "Bitstream Generation" 메뉴를 선택하고 "Programming Mode" 를 "SPI active x2" 로 변경해 줍니다.

변경된 Configuration Mode 에 맞추어 Bitstream File 을 다시 생성하여 사용하면 되겠습니다.

2. SPI Programming Clock Divider 값 변경.

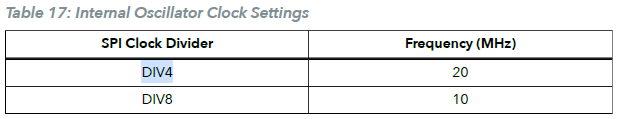

SPI Programming Clock Divider 값에 따라 SPI Click Frequency 가 아래와 같이 변경됩니다.

(참고문서 : https://www.efinixinc.com/docs/an006-configuring-trion-fpgas-v5.5.pdf )

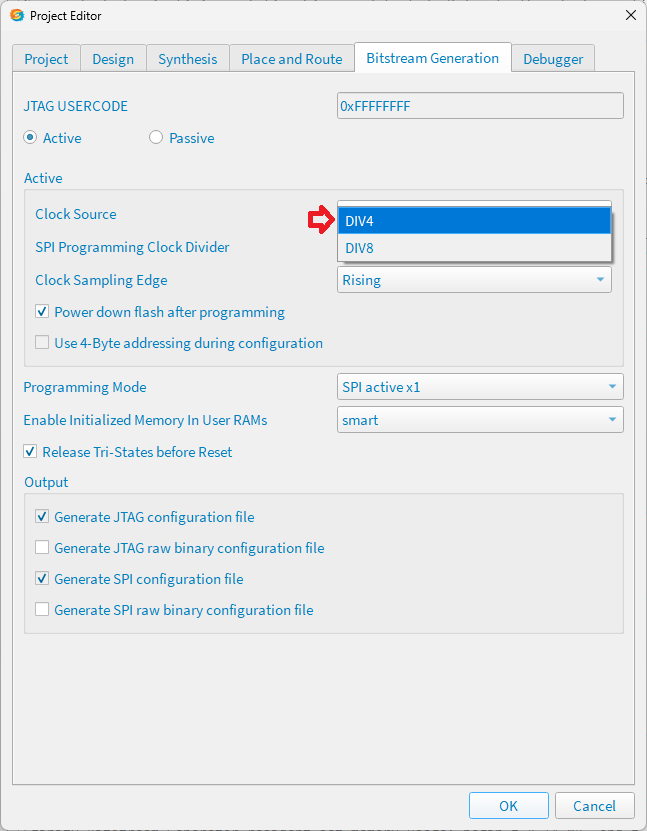

SPI Programming Clock Divider 값은 "Efinity IDE" 의 "Project Editor" 에서 변경할 수 있습니다.

"Project Editor" 를 실행한 후 "Bitstream Generation" 메뉴에서 "SPI Programming Clock Divider" 를 "DIV4" 로 변경해 줍니다.

마찬가지로 변경된 Option 에 맞추어 Bitstream File 을 다시 생성하여 사용하면 되겠습니다.